## Assessing the aggregate behavior of paralleled SiC Mosfets

Andrea Vinci, Technical Marketing, Tektronix

Wide Bandgap

Event 2025

Making WBG Designs Happen

A leading measurement insight company committed to performance and compelled by possibilities. Tektronix designs and manufactures test and measurement solutions to break through the walls of complexity and accelerate global innovation.

### **Tektronix**®

High-fidelity measurements, analysis and generation of high-speed signals with best-in-class **oscilloscopes**, **probes**, signal **sources**, **RF** measurement instruments, **software** and **services**.

- High signal frequencies up to 70 GHz

- Isolated Probing with Dynamic range up to +/-2.5KV

- Medium-range AC and DC measurements

- Voltage: mV's to kV

- Current: mA to 100's of amps

**Precision** instruments and systems for sourcing and measurement of analog voltage and currents suitable for **characterizing and validating power semiconductor devices**.

- Extremely precise DC measurements

- Voltage: nV to kV

- Current: fA to 10's of amps

- Medium-range DC power output in 10's or 100's of W

High-power efficient DC power supplies, bidirectional supplies, and electronic loads critical for development, test, simulation, and commercialization of products for tomorrow's electrified industries

- DC power outputs up to 3.84 MW

- DC voltage outputs up to 2000V

- DC Current outputs up to 64000A

- Regenerative loads return power to the grid at > 96% efficiency

78-year history

78-year history

50-year history

# Paralleled Mosfets Topologies WHY AND WHERE

#### Need:

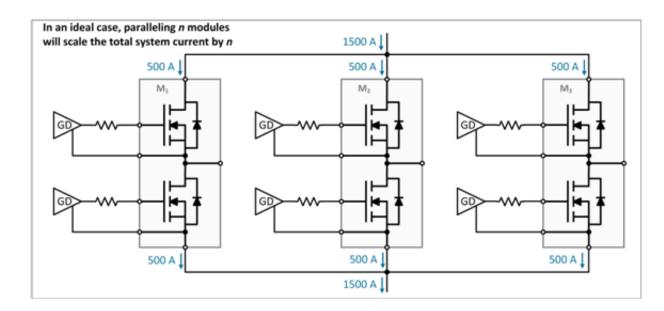

- Meet Increasing Power Demand -> Increase Current Capability

- Individual Current Rating is limited

- Dissipation capability is limited

- -> Mosfets Paralleling

### **Applications:**

- Solid-state switching in Power Distribution

- High Power DC-DC Converters, PFCs (AC/DC)

- Motor Drives and Inverters

- Protection Circuits in Battery Management

- Audio Amplifiers

- Induction Heating

# Paralleling Advantages of SiC MOSFETs Over IGBTs

- SiC MOSFETs often have a higher  $R_{\rm DS(ON)}$  temperature coefficient than Si IGBT  $V_{\rm CE}$  characteristics, which acts as a balancing mechanism when temperature imbalances exist

- SiC MOSFETs are more thermally conductive, allowing for better device-level heat dissipation and stable operating temperatures

- IGBTs have a steeper transconductance curve such that small changes in gate voltage near threshold have a larger effect on conduction as compared to SiC MOSFETs

# Current Sharing Challenges NOT A STRAIGHT FORWARD SOLUTION

### Theoretically it is necessary to:

- Ensure **balanced** static and dynamic currents

- Ensure even conduction and Switching Losses and Stresses

### Time consuming phase in:

- Precise simulation model and simulating condition environment

- Performing Validation with Test Equipment hardware and application software

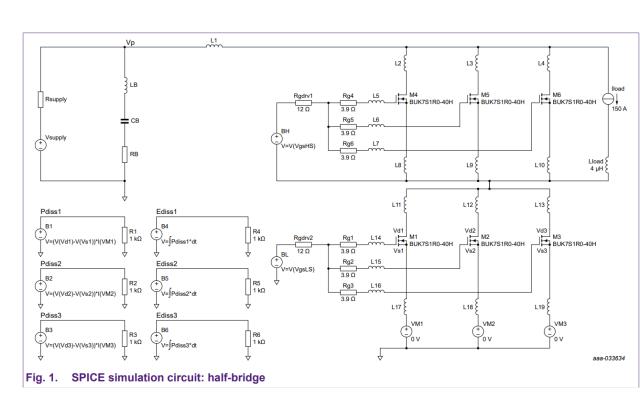

From Nexperia App Note: AN50005 Paralleling power MOSFETs in high power applications

## Paralleling is Not Perfect

## Ideal current sharing in the modules depends on various factors like:

- System layout- Parasitic inductance of commutation loop and gate loop, impedance of the load

- Gate driver configurations- Driving speed, timing delays can lead to circulating currents

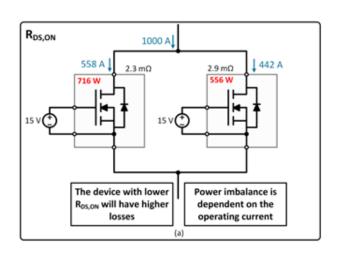

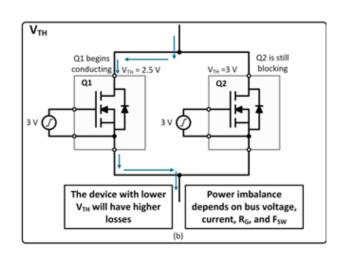

- Module parameter mismatch- Onstate resistance ( $R_{ds(on)}$ ) and threshold voltage ( $V_{th}$ )

- Heatsink configuration-Temperature imbalance can cause current imbalance

### Static:

Power Mosfets Static Rds ON has positive Temperature Coefficient

Plotting Rds ON and TJ and impact on Id over Time

### **Dynamic:**

Switching Over Stress -> Premature Failure • Transfer characteristics and transconductance matching!

# Strategies for Implementation according to Design Books

- Ultra symmetric layout. Match traces parasitic in simulation.

- Recogize linear orientation of switches and path.

- Easier for low voltage (gate driver), less easy for HV path

- Active Gate Control (gate voltage adjustment). Improves EMI

- Cons: Require current feedback, increases losses

- Inductance insertion in commutation path

- Cons: gate-source currents, voltage ringing, damages

- Need of shunts in series for drain current measurements

- Galvanic (optical) isolation of gate drivers (expensive)

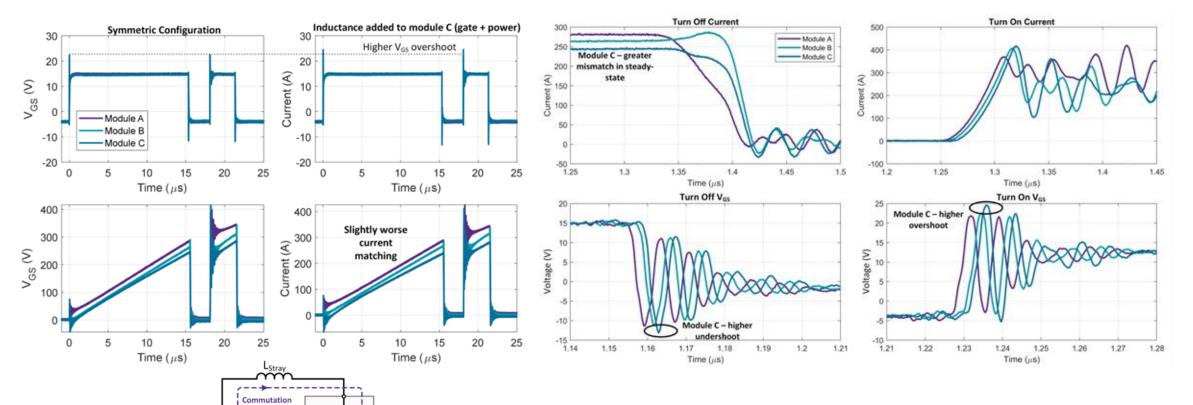

### **System Layout and Loop Inductance**

Path

- Module C has higher inductance added to the power loop and gate loop

- It results in slightly higher current unbalance but **less than 5**%

- Therefore, the system layout and loop inductance has **low impact** on Power Module paralleling

## Load Impedance Impact

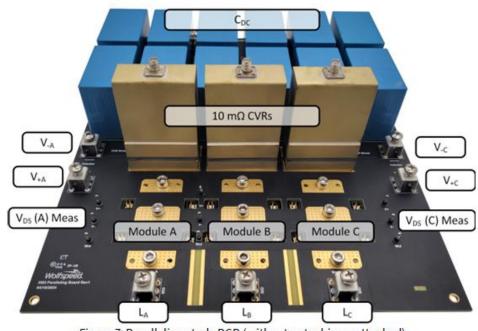

Figure 7: Paralleling study PCB (without gate drivers attached)

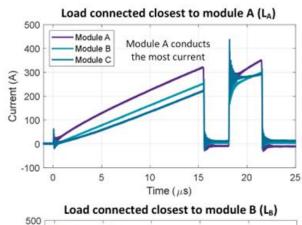

- The position of the load inductor is changed ( $L_A$ ,  $L_B$ , and  $L_C$ ) to add more inductance in path to the load from each module

- When the inductor is connected to  $L_A$ , the current through module A is significantly higher than through B or C

- As the load inductor is moved from  $L_A$  to  $L_B$  to  $L_C$ , the current through module A decreases and the current through module C increases

## **Gate Driver Configuration**

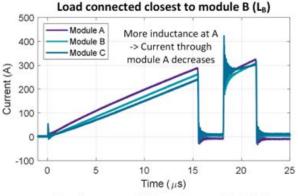

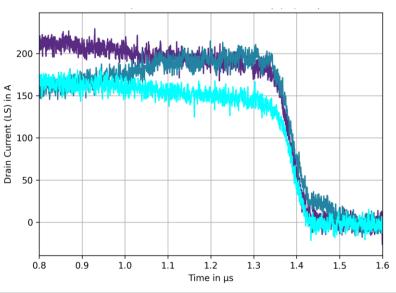

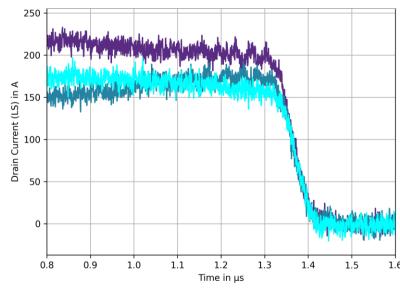

- The dynamic current matching and waveform quality is improved **significantly** with the common gate driver approach

- Inherent variation in signal timing and characteristics of components can cause significant imbalance between paralleled modules

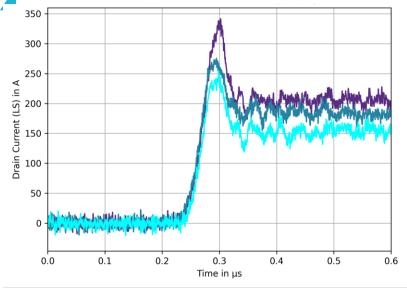

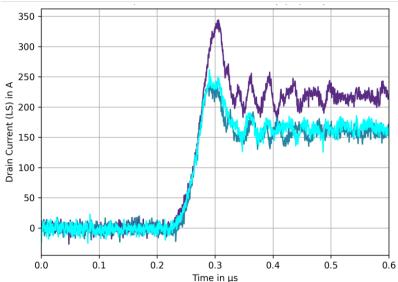

## Module Parameter Mismatch

# Summary of Factors Affecting Paralleling

| Design Parameter                   | Importance for<br>Dynamic Current<br>Sharing | Comments                                                                                                                                                                                         |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Loop Inductance<br>Imbalance | Low                                          | Power loop inductance should be minimized to reduce V <sub>DS</sub> overshoot, but has minimal affect current sharing                                                                            |

| Gate Loop Inductance<br>Imbalance  | Low                                          | Gate loop inductance should be minimized to reduce V <sub>GS</sub> overshoot, but has minimal affect current sharing                                                                             |

| Load Impedance Mismatch            | High                                         | Modules should have a symmetric attachment to the load.<br>Inserting inductance between each module and the load<br>can reduce mismatch. Connect midpoints at the load,<br>instead of at the bus |

| Gate Driver Implementation         | High                                         | Common gate driver implementations offer significantly better current sharing than distributed gate driver approaches. Propagation delay of signals                                              |

| Module Characteristics             | Medium                                       | Increased V <sub>TH</sub> imbalance between modules can increase dynamic mismatch. Before addressing this issue, ensure that the layout and gate driver implementations are optimized.           |

More details: Considerations for Current Balancing in Paralleled SiC Power Modules

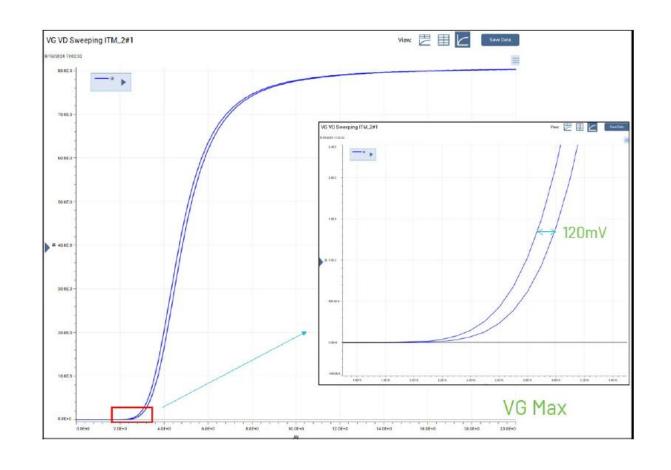

# Derive Precise Behavioral Models I-V AND C-V CHARACTERIZATION

### **Experimental PCB Validation**

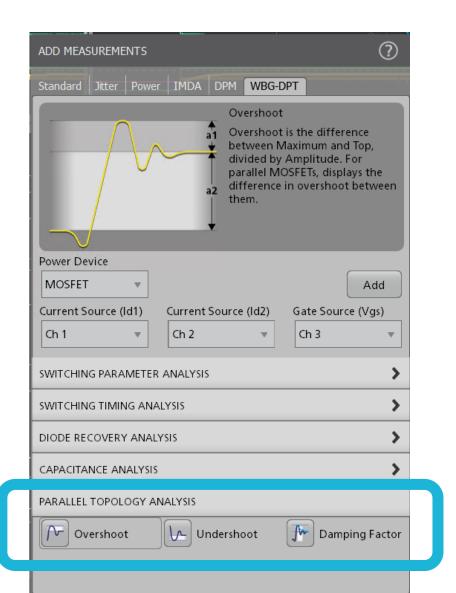

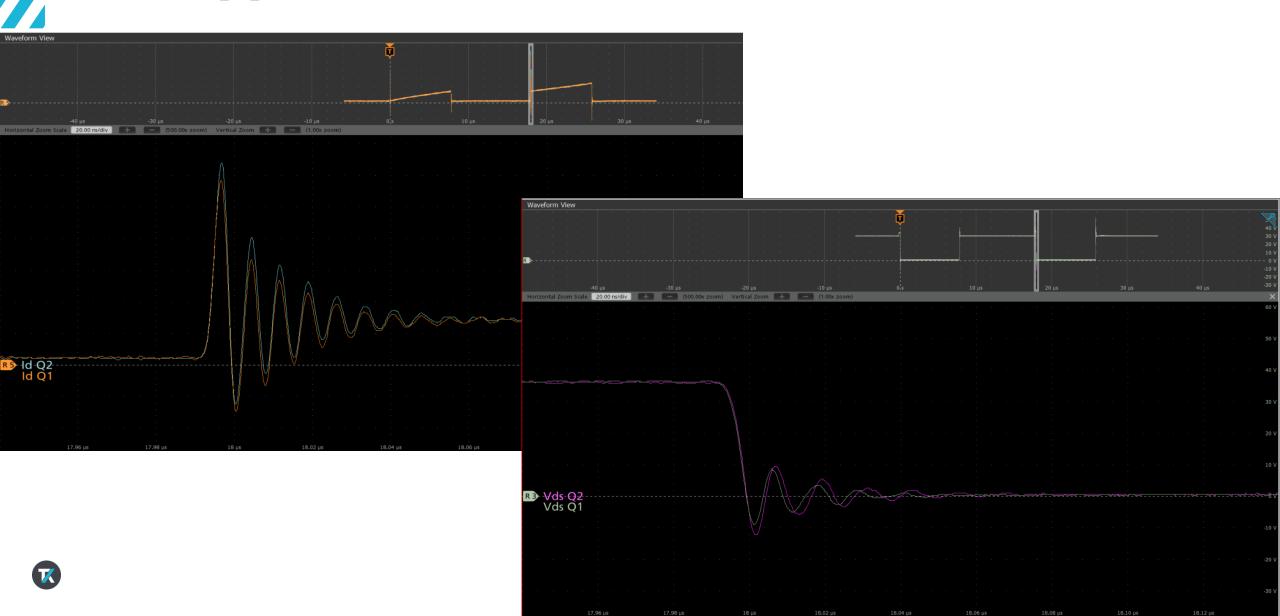

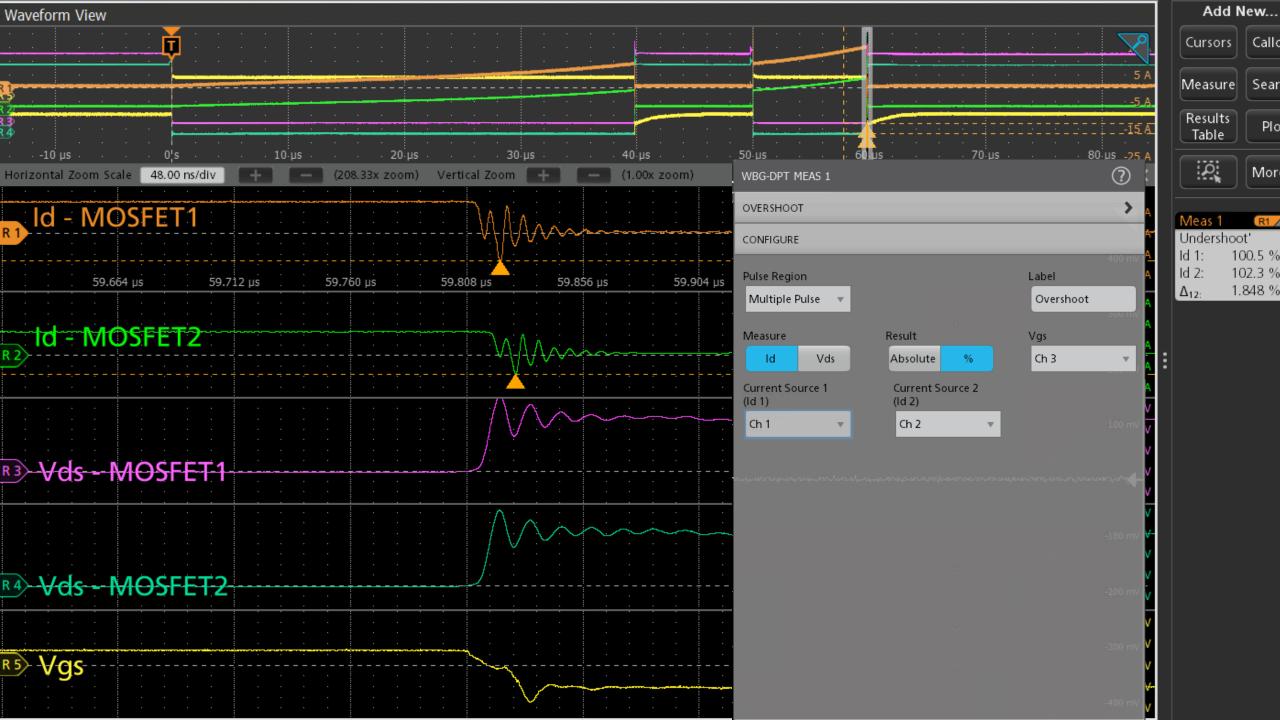

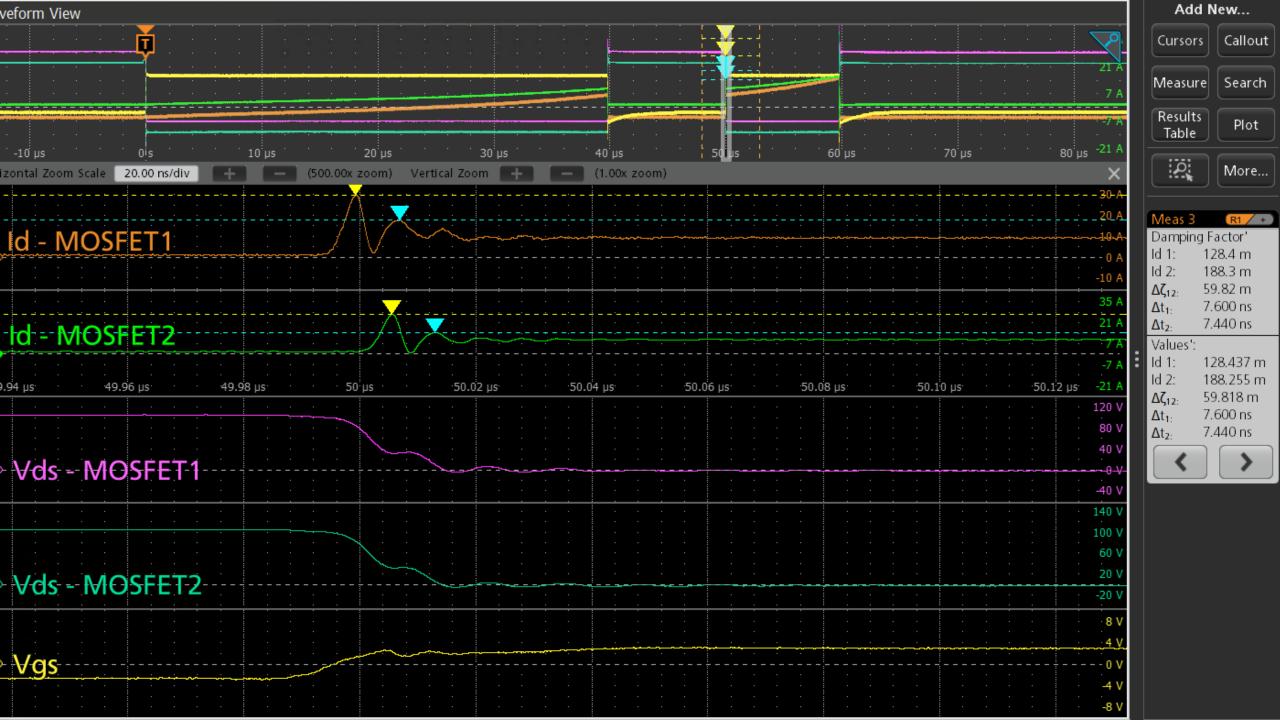

### A NEW DEDICATED SOFTWARE CAPABILITY

- Turn on / off waveforms under various load currents to detect current spikes and Vds variation rates

- Need multi-channel, high accuracy instrumentation and power probes

- Automated De-Skew

- Eon/Eoff

- Dead Time

- Overshoot/Undershoot Damping Factor

## **Overlapped Plots**

Andrea Vinci Technical Marketing

andrea.vinci@tek.com