Silicon Carbide JFETs enable breakthroughs of high-voltage solid state power distribution

Leo Aichriedler

Distinguished Engineer Application Marketing

Infineon Technologies Austria AG

Bodo's

Wide Bandgap

Event 2025

Making WBG Designs Happen

#### **Solid State Power Distribution**

Why to change a 100-year old, proven electro-mechanical concept

- Reduction of Fault isolation delay from >10 ms to <5 μs</li>

- Minimal current overshoot

- Reduced Distortion in the distribution grid

- Selectivity vs. Electronic Sources

- Smart Protection Mechanisms

- Auto-Retry / Failure Recovery

- Smart Inrush Handling

- Self Diagnostic

- Arc-Free, Wear-free Actuation and Protection

- Reduced Maintenance

- Installation Space (IT environment)

- Smart Load Control

- AC and DC compatible

- Size / Ampacity

- Power Dissipation

- Cost (CAPEX)

**Enabled by Power Semiconductor Solutions**

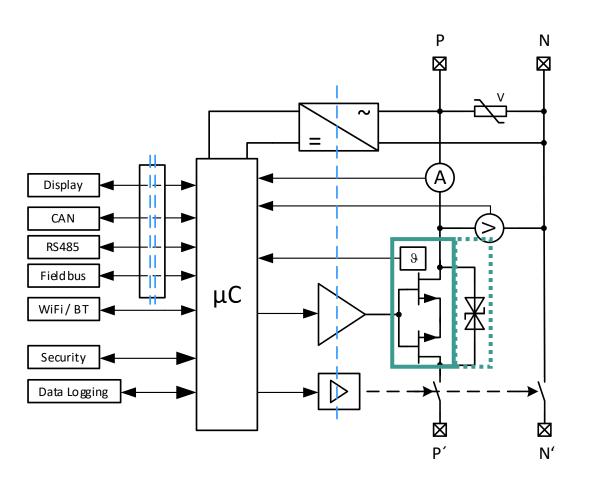

## Solid State Circuit Breakers from a System Perspective

Power Stage as critical building block

#### SSCB Requirement

- Very low Voltage drop @ rated current

- Overload Capability

- High Current Switching Capability

- Interplay with Clamping Device

- Overvoltage / Overcurrent Robustness

- Power Temperature Cycle Robustness

- Miniature Solution Size

- Lifetime equivalent to EM solution

# Example: 63A/800 Vdc

- 150 mV/Pole 2.3 m $\Omega$  total

- $-3x I_{nom} *2s$

- $I_{SD} = 1 kA$

- TVS

- OVC III

- 500kc @ 125 °C

- Equivalent to 63A MCB

- >20 years \* 24/7

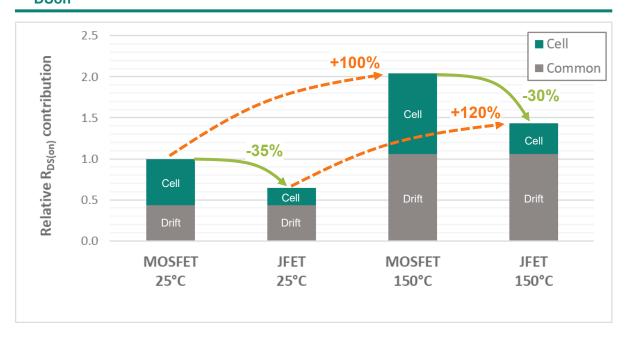

## JFET: Advancements in Ron\*A and FBSOA

#### R<sub>DSon</sub> Contribution: 1.2kV CoolSiC™ MOSFET vs. JFET

## Best-in-Class RDSon Ratings:

2.3m $\Omega$  @ 1200V V<sub>BDss</sub>

1.5m $\Omega$  @ 750V V<sub>BDss</sub>

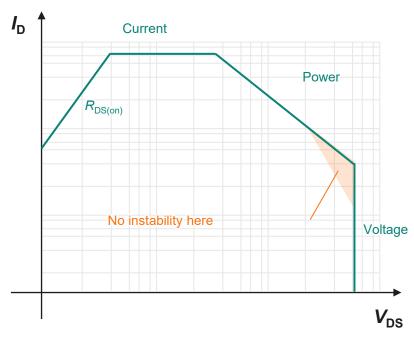

#### JFET FBSOA: ID vs. VDS

- Thermal Stability under all operating conditions

- No hot-spotting during overload pulses

- Linear mode capable

- Stable operation in "avalanche"

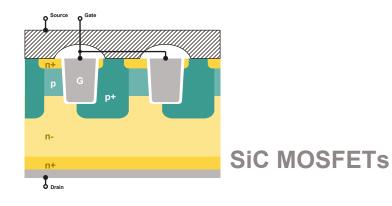

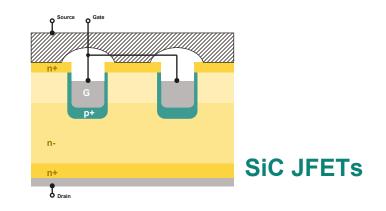

## **Technology differentiation – CoolSiC™ JFET vs. MOSFETs**

| Construction | Channel conduction, normally off Fully isolated gate Optimized for minimum gate feedback | Bulk conduction, normally on Non isolated gate Optimized for $R_{DS(on)}$ and robustness |

|--------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| FOMs         | Relatively high(er) R <sub>DS(on)</sub> Lower temperature coefficient                    | Lowest possible R <sub>DS(on)</sub> per device<br>Higher temperature coefficient         |

| Benefits     | Simplified control, high switching speed Compatibility to legacy circuits                | Maximum power density ** Active clamping ** Linear mode operation **                     |

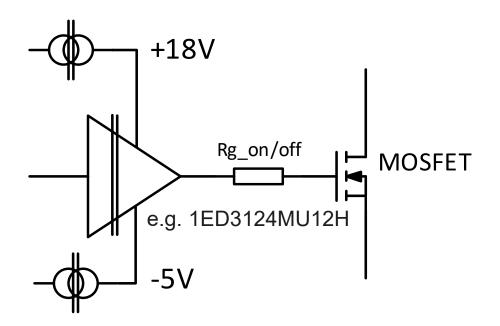

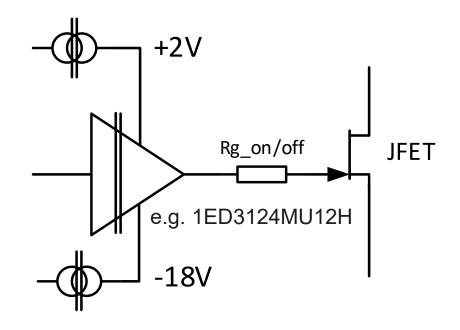

## **Driving a CoolSiC™ JFET is easy...**

Example: Isolated Gate Drive Scheme

- Exchange Polarity of Supply voltages: +18V → -18V; -5V → +2V

- Adoption of Rg\_on and Rg\_off values

- Use of same (basic) Gate Driver

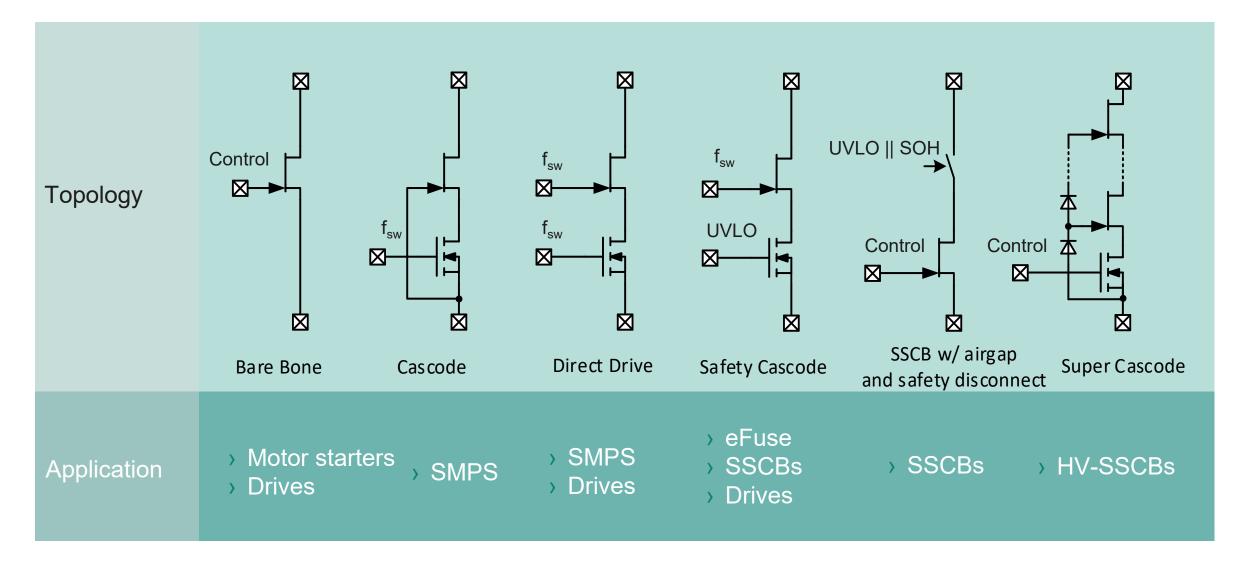

## Drive modes and application mapping for JFET/JFET Cascodes

## Package Optimization for full application performance

Q-DPAK enables efficient system integration into SSCB assemblies

#### Large Drain and Source interface area

- Minimize Losses

- Reduced current density at the interface

#### Optimized internal construction

- High current interfaces

- Diffusion soldering

- Large die area & internal paralleling

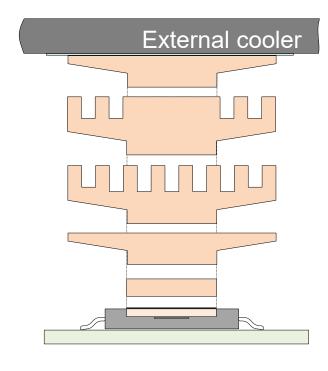

## Top-Side Cooling & large heatslug

- Lowest possible R<sub>th</sub>

- Directly connected, local C<sub>th</sub>

- Application-adjustable C<sub>th</sub>

- Directly attached TSC cooler enables flexibility

- Adjust i²t capability via C<sub>th</sub> extension

- Optimize R<sub>th</sub>

- Reduce Thermal cycling stress

## **Summary**

- Solid-State Power Distribution is a new emerging application field with special requirements to the applied semiconductors

- Ultra-Low RDSon of HV Power Transistors

- Robustness and Reliability under heavily exposed conditions

- The CoolSiC™ JFET enables high performance SSCB designs by

- Groundbreaking low R<sub>DSon</sub> values

- Simplified device paralleling

- High Current Avalanche Ratings to minimize the effort in clamping solutions

- The Q-DPAK Package is optimally suited for the implementation of high current SSCBs

- Large routing interface area on both, Drain and Source contacts

- Large thermal interface area

- User-extendable thermal capacitance for overload capability.