Paralleling SiC MOSFETs: a robust approach for high-power converter performance and thermal management

Salvatore La Mantia, Technical Marketing Manager, ST

Bodo's

Wide Bandgap

Event 2025

Making WBG Designs Happen

## SiC MOSFET - packaging

#### Research in advanced package technologies

Leadless packages **Enablers for miniaturization**

Leaded packages Std packages for economy of scale

**Top-side cooling SMD** Connected on heatsink for excellent cooling

> **Multisintering package** High reliability, high power density

> > Modular package Multipurpose configurations

**Bare dice** High-temperature or in-house assemblies

PowerFLAT 8x8 HV TO-LL

Q3'26

HiP247 HiP247-4 H2PAK-7 TO247-4 HC

**HU3PAK HC**

### SiC MOSFETs - Product Portfolio All P/N in Mass Production

1700V 45 mΩ

1700V 1.0  $\Omega$

1700 V

1200V 15  $m\Omega$

SCT015W120G3-4AG

1200V 16 m $\Omega$

SCT016H120G3AG

1200V 18.5 mΩ

SCT020HU120G3AG SCT020H120G3AG SCT020W120G3-4AG

1200V 19.2 mΩ

SCT019HU120G3AG SCT019H120G3AG SCT019W120G3-4AG

1200V 27  $m\Omega$

SCT025H120G3AG SCT025W120G3-4AG SCT025W120G3AG SCT025W120G3-4

1200V 40 mΩ

SCT040HU120G3AG SCT040H120G3AG SCT040W120G3AG SCT040W120G3-4AG SCT040W120G3-4

1200V 63 mΩ

SCT070HU120G3AG SCT070H120G3AG SCT070W120G3-4AG SCT070W120G3-4 SCT070W120G3AG SCT070H120G3-7

1200 V

Breakdown voltage (V

750V  $11m\Omega$

SCT011HU65G3AG SCT011H75G3AG

SCT012H90G3AG SCT012W90G3AG SCT012W90G3-4AG

750V 22 mΩ

SCT020H75G3AG

750V 29 mΩ

SCT029H75G3AG

750V 60 mΩ

SCT060HU75G3AG

750V - 900V

650V 13.5mΩ

SCT014HU65G3AG SCT014TO65G3

650V 20mΩ

SCT018HU65G3AG SCT018H65G3AG SCT018W65G3-4AG SCT018W65G3AG SCT018H65G3-7

650V 29mΩ

SCT027HU65G3AG SCT027H65G3AG SCT027TO65G3 SCT027W65G3-4AG

650V 40 mΩ

SCT040HU65G3AG SCT040H65G3-7 SCT040H65G3AG SCT040TO65G3 SCT040W65G3AG SCT040W65G3-4AG SCT040W65G3-4

650V 58 mΩ

SCT055HU65G3AG SCT055H65G3AG SCT055H65G3-7 SCT055TO65G3 SCT055W65G3-4AG

650 V

Rds ON  $(m\Omega)$

### **Power Switch Parallelization**

Why we talk about parallelization?

# Benefits of parallelization 1. Thermal

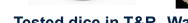

| Devices                          | Total Rdson<br>(Configuration)           | Equivalent Thermal resistance J-case | Equivalent<br>Thermal<br>resistance<br>case-heatsink* | Equivalent Total<br>thermal resistance<br>Junction-heatsink | ΔTj for each<br>100 W<br>Power<br>Losses |

|----------------------------------|------------------------------------------|--------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|

| SCT019HU120G3AG                  | <b>9.6 mΩ</b> (2 x 19.2mΩ in //)         | 0.15°C/W<br>(2 x 0.3 in //)          | 0.3°C/W<br>(2 x 0.6 in //)                            | 0.45°C/W<br>(2 device in //)                                | 45°C                                     |

| SCT025HU120G3AG                  | 13.5 m $\Omega$ (2 x 27m $\Omega$ in //) | 0.2°C/W<br>(2 x 0.4 in //)           | 0.3°C/W<br>(2 x 0.6 in //)                            | 0.5°C/W<br>(2 device in //)                                 | 50°C                                     |

| SCT040HU120G3AG                  | 20 m $\Omega$ (2 x 40m $\Omega$ in //)   | 0.25°C/W<br>(2 x 0.5 in //)          | 0.3°C/W<br>(2 x 0.6 in //)                            | 0.55°C/W<br>(2 device in //)                                | 55°C                                     |

| 9.6 m $\Omega$ 1200V (simulated) | 9.6 mΩ<br>1 x device in HU3PAK           | 0.2°C/W                              | 0.6°C/W                                               | 0.8°C/W<br>(one device)                                     | 80°C                                     |

Two devices in parallel provides significantly better thermal behavior than a single switch

# Results of best TIM material measurements for HU3PAK

1) 0.32 K/W Gap-Filler pad – 0.7mm thickness

2) 0.33 K/W Liquid Gap-Filler – 0.7mm thickness

3) 0.35 K/W Al<sub>2</sub>O<sub>3</sub> ceramics + Thermal paste + Counterplate – 1.0mm thickness

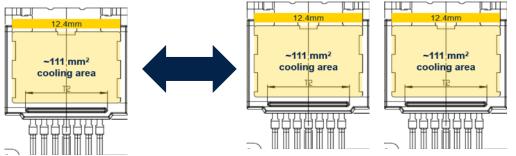

### Benefits of parallelization 2. Switching losses

Comparing 2 devices in parallel and single device with comparable RDSon 2 devices will generate lower switching losses

### Challenge

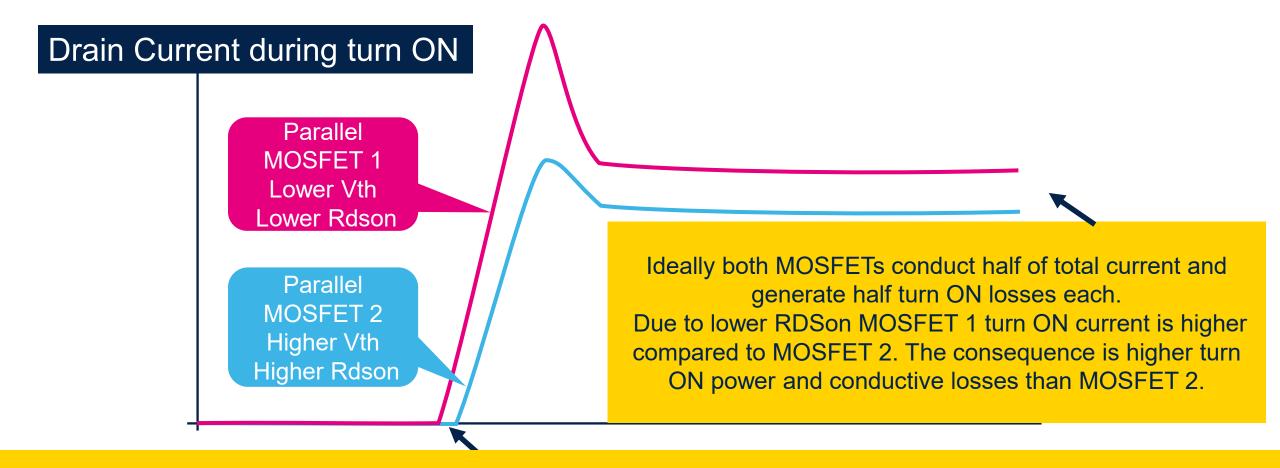

Vth and RDSon impact to switching losses Two MOSFETs in parallel – issue explanation

Ideally both MOSFETs conduct half of total current and generate half turn ON losses each.

Due to lower Vth MOSFET 1 turn ON early compared to MOSFET 2. The consequence is the current through

MOSFET 1 will be higher than expected and consequently will generates more turn ON power losses than MOSFET 2.

## Challenge Vth and RDSon difference

#### Vth difference

- Causes one device is turning ON/OFF earlier than other one thus conducting higher current during switching → This part generates higher switching losses

- At higher temperature Vth is lower it introduces positive feedback loop

#### RDSon difference

- Part with lower RDSon conducts more current. As conductive losses depends on the Irms square, this part generates more conductive losses

- RDSon is higher at higher temperature it introduces negative feedback loop

- Effect of unbalance can be also partly reduced by thermal "crosstalk"

- it introduces negative feedback loop

#

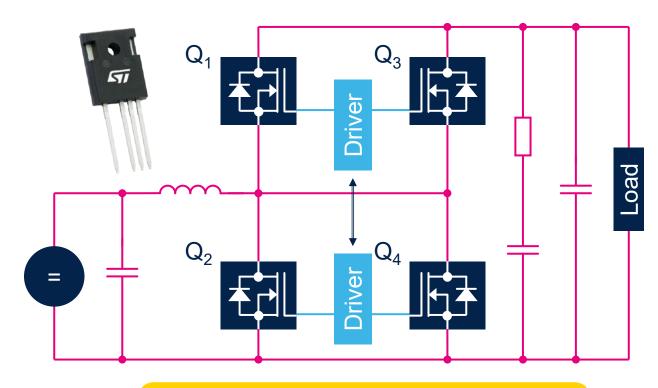

- SiC MOSFET 27m $\Omega$ , 1.2kV,

- Vth difference 350mV,  $\triangle$ RDSon 1.1m $\Omega$

- Configuration of step-up converter

- From 400 V<sub>DC</sub> to 800 V<sub>DC</sub> output up to 15kW

- All devices on same heatsink with thermal pads (electrically insulating)

- Defined contact pressure to the heatsink

- Measuring both V<sub>GS</sub> and V<sub>DS</sub> with optical isolated probes

- Monitoring temperature of heatsink, heatsink under each MOSFET as well as temperature of case of each device

| High                     | Vth                     | Low Vth                  |                         |  |

|--------------------------|-------------------------|--------------------------|-------------------------|--|

| R <sub>DS(on)</sub> [mR] | V <sub>GS(th)</sub> [V] | R <sub>DS(on)</sub> [mR] | V <sub>GS(th)</sub> [V] |  |

| 27.20                    | 3.063                   | 26.32                    | 2.750                   |  |

Monitoring especially low-side MOSFETs  $(Q_2, Q_4)$  as these are most stressed in this type of confugiration

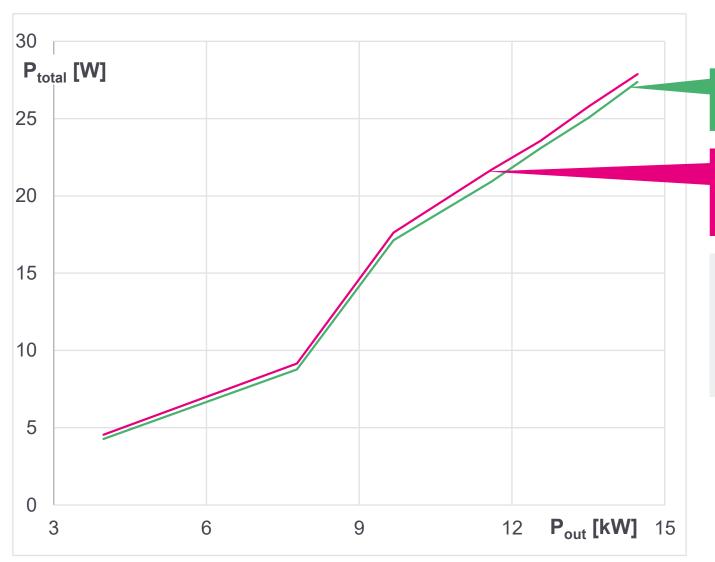

# AVth 350mV Practical example – Unbalanced Vth and RDSon ARDSon 1.1mo

Power losses of one device for ideal **conditions**. Vth of both parts is similar.

Power losses for one device of more stressed device for different Vth (350mV).

One device power losses between ideal condition and worse case condition was 0.5W (2%)

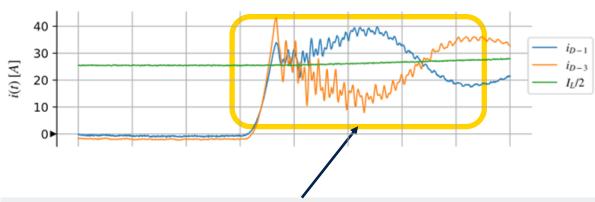

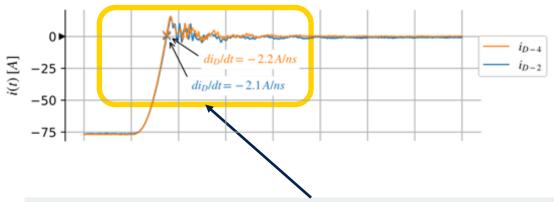

# Layout impact – tests with HU3PAK Comparison on signal level

Tur ON – current waveform Non ideal layout (2 layer)

Tur ON – current waveform Very good layout (4 layer)

Blue – Id through MOSFET 1 Orange – Id through MOSFET2

Significant unbalance and oscillation due to Vth difference and non ideal layout

Blue – Id through MOSFET 1 Orange – Id through MOSFET2

Thanks good layout the currents are in similar tracks even Threshold difference

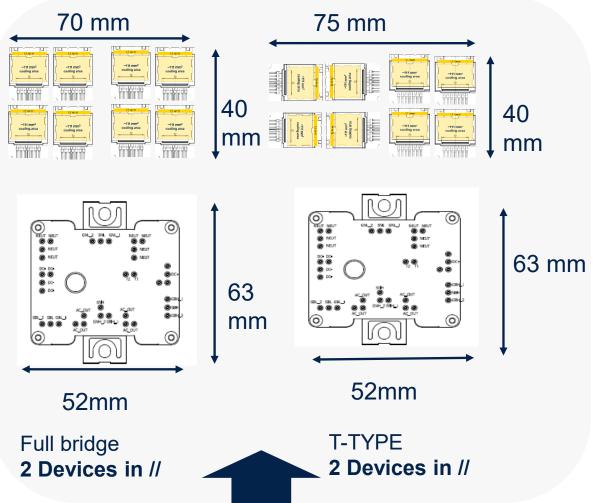

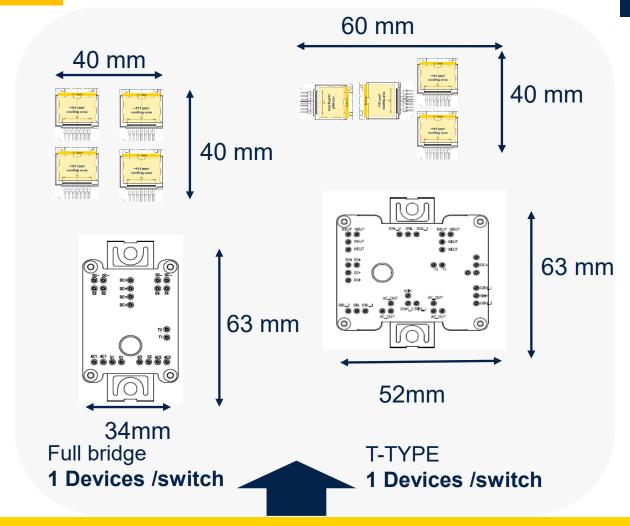

# SiC HU3PAK vs Power Module PCB Area layout examples

#### Discretes enable great flexibility vs design optimization

Parallel MOSFETs - Optimized for thermal resistance

Optimized for number of devices reduction (or interleaved solution)

## Conclusion

### Conclusion

- Parallelization allows to achieve higher power transfer thanks to:

- Reduction of thermal resistance to heatsink allowing to reduce device temperature

- Reduction of switching power losses (turn OFF)

- Parallelization allows using discretes for application typically covered by power modules

- Potentially Rth and Vth differences leads to different power but

- RDSon difference impact to conductive losses is naturally compensated by Rdsn vs thermal dependance

- Vth difference (for presented example) deviation between higher temperature device and ideal condition is in range of few %

- The good layout (reduction of commutation loop) helps to reduce Vth impact to current unbalance

# Our technology starts with You

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>.

All other product or service names are the property of their respective owners.